PROGRAMACION

PRACTICA CON PLC.

Crearemos una pequeña

aplicación que permita la partida retardada de la salida 0 del módulo 2 ante

la activación de la entrada 0 del módulo 1. El PLC a utilizar tiene las

siguientes características:

CPU

:

1747-L532 OS301

INPUT

: 2 Módulos 1747-IM16

OUTPUT

: 2 Módulos 1747-OW16

ANALOGA

: 1 Módulo

1747-NIO4I

FUENTE

: a determinar

RACK

: 1746-A7

Paso

1:

Elegimos el procesador que utilizaremos: File->new ->

Driver

:

Se define aquí el driver de comunicaciones a utilizar, por el momento en forma

off-line no es necesario indicarlo

Processor Node : Número de Nodo que identifica al PLC, solo es necesario cuando nos conectemos con él.

Who Active : Utilidad que permite buscar los nodos activos (PLC conectados al sistema)

Reply

Timeout

: Tiempo de espera máximo para la comunicación con el PLC.

Paso

2:

Configuramos nuestro sistema (Rack, I/O, Fuente, etc.)

Para esto basta hacer doble en I/O configuration de la estructura del procesador, la pantalla de configuración es la que se muestra en la siguiente figura. La lista de la derecha muestra las opciones disponibles, basta solo “pinchar” y “arrastrar” para configurar.

Power

Supply

: Seleccionamos la fuente adecuada para nuestro proyecto, es conveniente

seleccionarla una vez que seleccionamos todos las I/O.

ReadIO Config : Utilidad que nos permite leer desde el procesador la configuración existente.

Filter : Nos permite seleccionar que tarjetas queremos visualizar (todas, solo de entradas, etc.).

Hide All Card : Permite visualizar o no visualizar la lista de tarjetas disponibles.

Adv. Config : Nos permite una configuración avanzada (tiempos de scan, canales, etc.).

Paso

3:

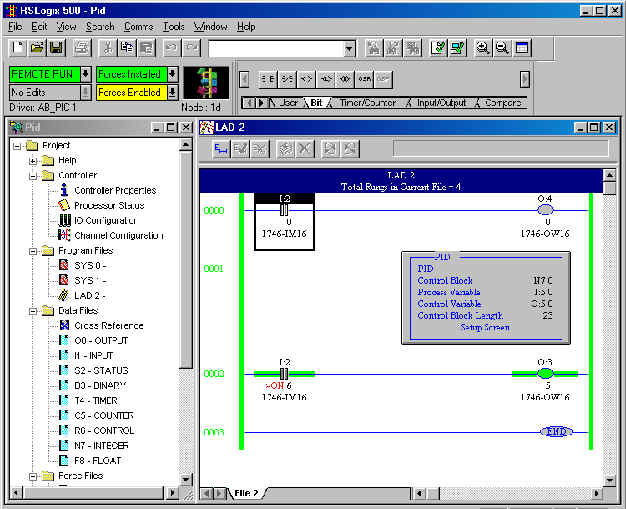

Construimos nuestro diagrama.

Debemos insertar nuestra

primera rama, para esto tenemos varias opciones:

Mediante la tecla INS.

Mediante el Menú Edit-Inssert Rung.

Usando el botón derecho del mouse.

Directamente con la tecla R, si esta seleccionada la ventana del diagrama en escalera.

El software quedará de la siguiente forma

Paso

4:

Verificar nuestro archivo:

En el menú

edit->verify

file o verify Proyect podemos verificar la integridad de nuestro

programa o de nuestro proyecto en general si este consta de varios programas.

Paso

5:

Guardar nuestro proyecto:

Paso

6:

Transferimos nuestro programa al PLC:

Primero debemos seleccionar un

driver apropiado para la transferencia de nuestro programa, esto depende

del tipo de conexión que dispongamos, para el ejemplo suponemos una

conexión mediante interface PIC.

Los drivers disponibles deben definirse previamente en RSlink para su utilización, como se muestra a continuación:

En RSlink à Communications->Configure Drives

En

Rslogix -> Comms-> Download Programs

Si existe ya un programa en el PLC el sistema nos

pedirá confirmación de la sobreescritura como aparece en la siguiente

figura.

Paso

7:

Visualizamos nuestro programa On-Line y Ponemos nuestro PLC en modo RUN

En

RSlogix

Comms->

Go Online

Comms->Mode->RUN

Paso

8:

Depuración y Verificación de Lógica

Una vez cargado nuestro programa en el PLC y estando este en modo RUN

corresponde la fase de depuración del programa y detección de errores, para

esta fase RSlogix dispone de varias herramientas muy útiles, entre las más

destacadas:

Ejecución sin activación de salidas

Ejecución paso a paso

Visualización de archivos

Forzado de Bits

Creación da tablas de datos de usuario

Referencias cruzadas

Creación de Mnemónicos y Comentarios

Paso

9 : Generación de Reportes

Paso

10 :

Respaldo de programas

Ejemplos

prácticos propuestos en modo off-line:

1.-

Agregar a programa creado anteriormente mnemónicos y comentarios en todos los

niveles.

2.-

Construir los programas desarrollados en las sesiones anteriores

3.-

Configurar en los módulos las opciones avanzadas

4.-

Construir programas básicos de uso de:

Timers

Contadores

Instrucciones de Salto

Instrucciones de Control

Señales y números análogos

Bloque PID

Otras instrucciones de interés