# Interrupts on PIC micro

# 1. Lesson1 - introduction

If you are becoming a pic-microcontroller user and all new things are puzzling you, starting with interrupts would be "the hell thing" because you'll have to manage with your own imagination all pic resources, to got the final goal, a functional and stabile circuit board. Usually all advices you'll heard from older pic-micro users would be: "can't you do it without interrupts ? " or " the interrupts are difficult for beginners ! ". If you are reading now this issue, it's supposed you have taken already a carefull look on your favorite pic-micro data sheet . If not, you are encourage to do it, because everything you need to know is there. I will try just to clarify some interrupt aspects for your eyes ( and mine too…) in six practical lessons. It's also supposed, you are familiar with JAL language for PIC-microcontrollers, you have already at least a blinking led running, resulted as your own program writing, compiling and PIC programming or much better, you have already connected your PIC with your own PC and talking between those without major breakdowns on your RS232 interface… If you don't know nothing about all these, you may got some information browsing here:

- <u>http://www.voti.nl/jal/</u>

- <u>http://www.geocities.com/vsurducan/electro/PIC/pic.htm</u>

- <u>http://groups.yahoo.com/group/jallist/files/</u>

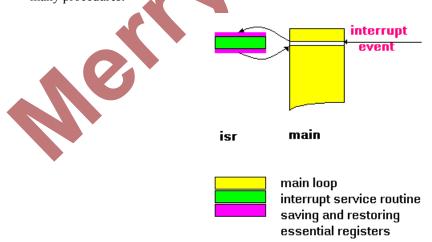

Your first rightful ask would be: "Why we need interrupts?" The answer it's easy: because the PIC microcontroller it's stupid. "Should I choose then another microcontroller ? " No, because all microcontrollers are stupidus ! Only the user it's clever. PIC microcontroller is doing ( almost like your PC ) only one thing once. Don't try to ask him to solve two different problems in the same time, will not be possible. For this purpose you need a multi-PIC scheme. But PIC microcontrollers can stop it's own principal program execution ( called **main or main loop** because here are chained all instructions which will run almost all of your tasks ) and run a small program branch ( called **interrupt service routine** because is launched by an **interrupt event** and usually it has a shorter length and is doing only a few things, opposite to main which have a considerable length ). Because for hobbists and beginners, only flash midrange PIC-micro are user-friendly usable, having the greatest feature of being reprogramable [while are running: PIC16F87xA, PIC16F87x, or not: PIC16F7x, PIC16F62x, PIC16F8x, PIC12FXXX ], I will talk only about interrupts on those. For these microcontrollers, the interrupt service routine will began always from the same address called **interrupt vector address** ( address 04 ). Fortunately ( or not?) for the user, can be only one Interrupt Service Routine, even the program running inside the ISR may be splitted in many procedures.

Figure 0-1 The interrupt mechanism

In JAL, the interrupt service routine must be written inside a procedure's body, the name of the procedure it's irrelevant because **will not be called** by another main procedures. The only reason why this procedure is necessary is to keep the **pragma interrupt** instruction. When the compiler find this instruction will put the assembled code written after this pragma at address 04. That's the replacement for **org 04h** directive in assembler to put the code ( or the call instruction ) at the interrupt vector address.

The problems are just begans. As you may know there are three extremely important registers ( between the other 54 different registers in PIC16F877 or just 28 different registers in PIC12F675 ) : w register ( the accumulator's result storage register), status register ( containing flags of mathematic operations and bank switching bits ) and the FSR register ( containing 8 address bits for indirect addressing ). If you have downloaded at least the JAL04.50 compiler all things are clear if you have inspected the assembler code resulted after a program compilation . If not, do it now after you'll compile the following jal lines:

```

include 16f84_4

include jpic

procedure whats_new_Stan is

pragma interrupt

end procedure

```

The essential compilation result would be the next one, which have the necessary translation for used registers names in the right colum:

| ORG 0004<br>movwf H'<br>swapf H'<br>clrf H'<br>movwf H' | 0C'<br>03',w<br>03'<br>0D' | ;<br>;<br>; | ; SAVING ESSENTIAL REGISTERS (PUSH)<br>; movwf temporary_w<br>; swapf status,w<br>; clrf status<br>; movwf temporary_status |

|---------------------------------------------------------|----------------------------|-------------|-----------------------------------------------------------------------------------------------------------------------------|

| movfw H'                                                |                            |             | ; movfw pclath                                                                                                              |

| movwf H'                                                |                            |             | movwf temporary_pclath                                                                                                      |

| clrf H'                                                 |                            | · /         | clrf pclath                                                                                                                 |

| movfw H'                                                |                            | • /         | movfw FSR                                                                                                                   |

| movwf H'                                                |                            | ;           | movwf temporary_FSR                                                                                                         |

| goto<br>ORG 000E                                        | Incerrupt                  |             |                                                                                                                             |

| interrupt:                                              |                            |             | interrupt upor godo                                                                                                         |

|                                                         |                            | i           | ; interrupt user code                                                                                                       |

|                                                         | new stan: ; 000E           |             |                                                                                                                             |

|                                                         | new stan: ; 000E           |             |                                                                                                                             |

|                                                         | _                          | ;           | RESTORING THE ESSENTIAL REGISTERS (POP)                                                                                     |

| movfw H'                                                |                            |             | movfw temporary FSR                                                                                                         |

|                                                         |                            |             | movwf FSR                                                                                                                   |

| movfw H'                                                | 0E'                        | ;           | movfw temporary pclath                                                                                                      |

| movwf H'                                                |                            |             | ; movwf pclath                                                                                                              |

| swapf H'                                                | 0D',w                      | ;           | ; swapf temporary_status, w                                                                                                 |

| movwf H'                                                | 03'                        | ;           | ; movwf status                                                                                                              |

| swapf H'                                                | 0C',f                      | ;           | ; swapf temporary_w, f                                                                                                      |

| swapf H'                                                | 0C',w                      | ;           | ; swapf temporary_w, w                                                                                                      |

| retfie                                                  |                            | ;           | ; retfie                                                                                                                    |

| main: ; 00                                              | 17                         |             |                                                                                                                             |

The first observation it's the abuse of usage for *swapf* instruction. Jumping to the instruction set description of any PIC microcontroller, *swapf* shows there are no status flags affected by this instruction. The reason why it's used here, is because is not modifying the status register while saving and restoring the

other essential registers. For PIC microcontrollers having less than 2Kbytes memory pages ( like PIC12F629/675, PIC16F84 or PIC16F62x) saving and restoring pclath it's not necessary. That's because the Program Counter in PIC arhitecture has 13 bits wide, splitted in Program Counter Low and Program Couter High. Only PCL its readable and writable. The PCH it's writable only via PCLATH register. Any *call* or *goto* instructions provide only 11 bits of address and allow branching within any 2K program memory page. The upper two bits of the address are provided by PCLATH bites 4 and 3. Those two are essential in PICs having 4K program memory (PIC16F873/874 PIC16F73/74) or 8K program memory ( PIC16F876/877 PIC16F76/77) because are addressing the desired program memory page. However the PC is pushed onto the 8 level stack every time a *call* instruction is executed or an interrupt causes a branch but PCLATH is not affected by a push or a pop operation. Note, there is no physical *push* or *pop* instructions, but a sequence of saving-restoring which is used any time an interrupt occure, as the last assembler code shows. Another important thing is the *retfie* instruction at the end of the pop sequence which allways enables all unmasked interrupts by seting the *intcon gie* flag. So the interrupts are native enabled in PIC micro arhitecture, only after the first interrupt has ocured and the ISR was readed. It's obviously clear you need to enable the interrupts for the first time somewhere inside the main; ( the **main** program it contains a definition sequence (includes, register definitions) and the **main loop** (forever loop, end loop) sequence )), else your interrupt routine will not work at all. The ISR can be placed anywhere in the main, except in the **main loop**, and only after the registers used inside the ISR are defined.

Let's see which are the most important registers dealing with interrupts in PICmicro midrange arhitecture, first one is the INTCON register:

| , | R/W-0 | R/W-x |  |

|---|-------|-------|-------|-------|-------|-------|-------|-------|--|

|   | GIE   | PEIE  | TOIE  | INTE  | RBIE  | TOIF  | INTF  | RBIF  |  |

|   | bit 7 | l.    |       | 1     |       |       |       | bit 0 |  |

| bit 7 | GIE: Global Interrupt Enable bit                                                                                                                                                                                          |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | 1 = Enables all unmasked interrupts                                                                                                                                                                                       |

|       | 0 = Disables all interrupts                                                                                                                                                                                               |

| bit 6 | PEIE: Peripheral Interrupt Enable bit                                                                                                                                                                                     |

|       | 1 = Enables all unmasked peripheral interrupts                                                                                                                                                                            |

|       | 0 = Disables all peripheral interrupts                                                                                                                                                                                    |

| bit 5 | T0IE: TMR0 Overflow Interrupt Enable bit                                                                                                                                                                                  |

|       | 1 = Enables the TMR0 interrupt                                                                                                                                                                                            |

|       | 0 = Disables the TMR0 interrupt                                                                                                                                                                                           |

| bit 4 | INTE: RB0/INT External Interrupt Enable bit                                                                                                                                                                               |

|       | 1 = Enables the RB0/INT external interrupt                                                                                                                                                                                |

|       | 0 = Disables the RB0/INT external interrupt                                                                                                                                                                               |

| bit 3 | RBIE: RB Port Change Interrupt Enable bit                                                                                                                                                                                 |

|       | 1 = Enables the RB port change interrupt                                                                                                                                                                                  |

|       | 0 = Disables the RB port change interrupt                                                                                                                                                                                 |

| bit 2 | T0IF: TMR0 Overflow Interrupt Flag bit                                                                                                                                                                                    |

|       | 1 = TMR0 register has overflowed (must be cleared in software)                                                                                                                                                            |

|       | 0 = TMR0 register did not overflow                                                                                                                                                                                        |

| bit 1 | INTF: RB0/INT External Interrupt Flag bit                                                                                                                                                                                 |

|       | 1 = The RB0/INT external interrupt occurred (must be cleared in software)                                                                                                                                                 |

|       | 0 = The RB0/INT external interrupt did not occur                                                                                                                                                                          |

| bit 0 | RBIF: RB Port Change Interrupt Flag bit                                                                                                                                                                                   |

|       | 1 = At least one of the RB7:RB4 pins changed state; a mismatch condition will continue to set<br>the bit. Reading PORTB will end the mismatch condition and allow the bit to be cleared<br>(must be cleared in software). |

|       | 0 = None of the RB7:RB4 pins have changed state                                                                                                                                                                           |

|       |                                                                                                                                                                                                                           |

### Figure 0-2 INTCON register

The *intcon\_gie* flag must be enabled any time when we are reading an interrupt event and be disabled when the interrupts are interfering with our program branch. One example is writing a long message on the 4 rows, 20 characters LCD when the button read interrupts are enabled. The effect will be a stop in LCD writing when the reading button interrupt sequence its reached ( as will see in Lesson2 Disabling interrupts. When? ). The writing will continue after one button it's pushed. The cause of this malfunction is the time length necessary for LCD writing which is longer than button reading refresh rate. Solution: disable interrupts while the whole message are writted on the LCD or increase the refresh rate for buttons. Last choice is not applicable, because the refresh rate is usually set between 10mS and 60mS and writing on a lazy LCD can take much longer.

The *intcon\_peie* flag may be used any time we are dealing with peripheral interrupts. The interrupt logic diagram of any PIC microcontroller will show us who are the peripheral interrupts:

The source of interrupts which can be masked by *intcon\_peie* are dependent by microcontroller resources, in PIC16F628 they are:

- TiMeR1 Interrupt,

- TiMeR2 Interrupt,

- CompareCapturePwm1 Interrupt,

- CoMparator Interrupt,

- Universal Synchronously Asynchronously Receiver Transmiter Transmit Interrupt (TXI),

- USART Receive Interrupt (RXI),

- EEprom write operation Interrupt

PIC16F877A have the same peripheral interrupts like PIC16F628 and a few more:

- Analogic Digital module Interrupt

- Compare Capture Pwm2 Interrupt

- Synchronous Serial Port Interrupt

- Parallel Slave Port read-writeInterrupt

- **Bus CoLision Interrupt**

PIC12F675 have the same peripheral interrupts as PIC16F628 except the USART interrupts because there is no USART module in PIC12F675.

All those interrupt sources have two special bits: the Flag bit and the Enable bit. The enable bit allows the interrupt to be set and the flag bit allows to read the effect of the interrupt. The flag bit must usually be cleared in software. Except for the interrupts which can be found inside the *intcon* register, the peripheral interrupts are defined by PIE registers ( for Enabling the interrupts ) and PIR registers ( for reading the

interrupts effect via Flags ). For the PIC16F877 there are two PIR and two PIE registers which are described below:

|       | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | R/W-0         | R-0                                          | R-0           | R/W-0         | R/W-0       | R/W-0          | R/W-0  |  |  |  |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|----------------------------------------------|---------------|---------------|-------------|----------------|--------|--|--|--|

|       | PSPIF <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ADIF          | RCIF                                         | TXIF          | SSPIF         | CCP1IF      | TMR2IF         | TMR1IF |  |  |  |

|       | bit 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |               | •                                            |               |               | •           |                | bit 0  |  |  |  |

| bit 7 | <ul> <li>PSPIF<sup>(1)</sup>: Parallel Slave Port Read/Write Interrupt Flag bit</li> <li>1 = A read or a write operation has taken place (must be cleared in software)</li> <li>0 = No read or write has occurred</li> <li>ADIF: A/D Converter Interrupt Flag bit</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |               |                                              |               |               |             |                |        |  |  |  |

| bit 6 | ADIF: A/D Converter Interrupt Flag bit<br>1 = An A/D conversion completed<br>0 = The A/D conversion is not complete                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |               |                                              |               |               |             |                |        |  |  |  |

| bit 5 | RCIF: USART Receive Interrupt Flag bit<br>1 = The USART receive buffer is full<br>0 = The USART receive buffer is empty                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |               |                                              |               |               |             |                |        |  |  |  |

| bit 4 | <b>TXIF</b> : USART Transmit Interrupt Flag bit<br>1 = The USART transmit buffer is empty<br>0 = The USART transmit buffer is full                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |               |                                              |               |               |             |                |        |  |  |  |

| bit 3 | <ul> <li>SSPIF: Synchronous Serial Port (SSP) Interrupt Flag</li> <li>1 = The SSP interrupt condition has occurred, and must be cleared in software before returning from the Interrupt Service Routine. The conditions that will set this bit are: <ul> <li>SPI</li> <li>A transmission/reception has taken place.</li> </ul> </li> <li>I<sup>2</sup>C Slave <ul> <li>A transmission/reception has taken place.</li> </ul> </li> <li>I<sup>2</sup>C Master <ul> <li>A transmission/reception has taken place.</li> </ul> </li> <li>I<sup>2</sup>C Master <ul> <li>A transmission/reception has taken place.</li> </ul> </li> <li>I<sup>2</sup>C Master <ul> <li>A transmission/reception has taken place.</li> </ul> </li> <li>I<sup>2</sup>C Master <ul> <li>A transmission/reception has taken place.</li> </ul> </li> <li>The initiated START condition was completed by the SSP module.</li> <li>The initiated Restart condition was completed by the SSP module.</li> <li>The initiated Acknowledge condition was completed by the SSP module.</li> <li>A START condition occurred while the SSP module was idle (Multi-Master system).</li> <li>A STOP condition occurred while the SSP module was idle (Multi-Master system).</li> </ul> |               |                                              |               |               |             |                |        |  |  |  |

| bit 2 | <ul> <li>0 = No SSP interrupt condition has occurred.</li> <li>CCP1IF: CCP1 Interrupt Flag bit</li> <li><u>Capture mode:</u></li> <li>1 = A TMR1 register capture occurred (must be cleared in software)</li> <li>0 = No TMR1 register capture occurred</li> <li><u>Compare mode:</u></li> <li>1 = A TMR1 register compare match occurred (must be cleared in software)</li> <li>0 = No TMR1 register compare match occurred (must be cleared in software)</li> <li>0 = No TMR1 register compare match occurred (must be cleared in software)</li> <li>0 = No TMR1 register compare match occurred</li> <li><u>PWM mode:</u></li> <li>Unused in this mode</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |               |                                              |               |               |             |                |        |  |  |  |

| bit 1 | 1 = TMR2 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | to PR2 mate   | Match Inter<br>ch occurred<br>natch occurr   | (must be cle  |               | ware)       |                |        |  |  |  |

| bit 0 | 1 = TMR1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | register over | ow Interrupt<br>rflowed (mus<br>not overflow | st be cleared | d in software | è)          |                |        |  |  |  |

|       | Note 1: F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | SPIF is res   | erved on PI                                  | C16F873/87    | 6 devices; a  | lways maint | ain this bit c | lear.  |  |  |  |

## Figure 0-4 PIR1 register in PIC16F877

|       | R/W-0                                    | R/W-0          | R/W-0         | R/W-0         | R/W-0           | R/W-0  | R/W-0  | R/W-0  |  |

|-------|------------------------------------------|----------------|---------------|---------------|-----------------|--------|--------|--------|--|

|       | PSPIE <sup>(1)</sup>                     | ADIE           | RCIE          | TXIE          | SSPIE           | CCP1IE | TMR2IE | TMR1IE |  |

|       | bit 7                                    |                |               |               |                 |        |        | bit 0  |  |

|       |                                          |                |               |               |                 |        |        |        |  |

| bit 7 | PSPIE <sup>(1)</sup> : F                 | Parallel Slave | e Port Read   | d/Write Inter | rupt Enable bit |        |        |        |  |

|       | 1 = Enables the PSP read/write interrupt |                |               |               |                 |        |        |        |  |

|       |                                          | es the PSP r   |               |               |                 |        |        |        |  |

| bit 6 | ADIE: A/D                                | Converter Ir   | nterrupt Ena  | able bit      |                 |        |        |        |  |

|       |                                          | s the A/D co   |               |               |                 |        |        |        |  |

|       | 0 = Disable                              | es the A/D co  | onverter inte | errupt        |                 |        |        |        |  |

| bit 5 |                                          | RT Receive     |               |               |                 |        |        |        |  |

|       |                                          | s the USAR     |               |               |                 |        |        |        |  |

|       |                                          | es the USAR    |               | •             |                 |        |        |        |  |

| bit 4 |                                          | RT Transmi     |               |               |                 |        |        |        |  |

|       |                                          | s the USAR     |               |               |                 |        |        |        |  |

|       |                                          | es the USAR    |               |               |                 |        |        |        |  |

| bit 3 | 1                                        | nchronous S    |               | nterrupt Ena  | ible bit        |        |        |        |  |

|       |                                          | s the SSP ir   |               |               |                 |        |        |        |  |

|       |                                          | es the SSP i   |               |               |                 |        |        |        |  |

| bit 2 |                                          | CP1 Interru    |               | it            |                 |        |        |        |  |

|       |                                          | s the CCP1     |               |               |                 |        |        |        |  |

|       |                                          | es the CCP1    |               |               |                 |        |        |        |  |

| bit 1 |                                          | MR2 to PR2     |               |               |                 |        |        |        |  |

|       |                                          | s the TMR2     |               |               |                 |        |        |        |  |

|       |                                          | es the TMR2    |               |               | t               |        |        |        |  |

| bit 0 |                                          | MR1 Overflo    |               |               |                 |        |        |        |  |

|       |                                          | s the TMR1     |               |               |                 |        |        |        |  |

|       |                                          | es the TMR1    | overnow in    | iterrupt      |                 |        |        |        |  |

Note 1: PSPIE is reserved on PIC16F873/876 devices; always maintain this bit clear.

## Figure 0-5 PIE1 register in PIC16F877

All peripheral interrupts bits are quite clear described in those PIE-PIR registers. The user must set first the enable bit coresponding to the interrupts which will be used and then to read the coresponding flag bit and detetect the interrupt event inside the ISR. The only problem which the user may have, would be to choose the right reading sequence without loosing any asynchronously event. This will not be easy for multiple interrupts events (or chained interrupts events) which must be detected. A good rule is to disable the specific interrupts, while inside the ISR that interrupt event is treated, else ( especially for fast events) the program may loop in a false forever loop ( because of an interrupt event which is taking place inside the same interrupt branch while the last interrupt is treated )

Going back to *intcon* register, there were left also three interrupts sources:

Tmr0 Interrupt

• **INT** RB0/INT external Interrupt

• **RBI RB** Port Change Interrupt

TMR0 interrupt is the most frequently used interrupt for small time events detection. TMR0 is an 8 bit wide register having also a prescaler setable with 8 different rates from 1:2 to 1:256. The prescaler must be understood as a divider register. The TMR0 register will be incremented one step, from the value which has been previously written, every time when the prescaler has overflow. When TMR0 has overflow the coresponding *intcon\_t0if* flag will be set. Inspecting this flag, use the low to high transition of the flag in conjunction with other time dependent events ( ie: reading buttons, increment a real time clock register ) and reseting the flag, it's an user defineable problem.

bit 0

|         | U-0                                                                                                                                                          | R/W-0            | U-0               | R/W-0         | R/W-0           | U-0         | U-0          | R/W-0  |  |  |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------------------|---------------|-----------------|-------------|--------------|--------|--|--|

|         |                                                                                                                                                              | Reserved         | —                 | EEIF          | BCLIF           | _           | —            | CCP2IF |  |  |

|         | bit 7                                                                                                                                                        |                  |                   |               |                 |             |              | bit 0  |  |  |

|         |                                                                                                                                                              |                  |                   |               |                 |             |              |        |  |  |

| bit 7   | Unimplem                                                                                                                                                     | nented: Read     | as '0'            |               |                 |             |              |        |  |  |

| bit 6   | Reserved: Always maintain this bit clear                                                                                                                     |                  |                   |               |                 |             |              |        |  |  |

| bit 5   | Unimplemented: Read as '0'                                                                                                                                   |                  |                   |               |                 |             |              |        |  |  |

| bit 4   | EEIF: EEP                                                                                                                                                    | ROM Write C      | peration I        | nterrupt Flag | g bit           |             |              |        |  |  |

|         | <ul> <li>1 = The write operation completed (must be cleared in software)</li> <li>0 = The write operation is not complete or has not been started</li> </ul> |                  |                   |               |                 |             |              |        |  |  |

| bit 3   | BCLIF: Bu                                                                                                                                                    | is Collision Int | errupt Fla        | g bit         |                 |             |              |        |  |  |

|         | <ul> <li>1 = A bus collision has occurred in the SSP, when configured for I2C Master mode</li> <li>0 = No bus collision has occurred</li> </ul>              |                  |                   |               |                 |             |              |        |  |  |

| bit 2-1 | Unimplem                                                                                                                                                     | nented: Read     | as '0'            |               |                 |             |              |        |  |  |

| bit 0   | CCP2IF: CCP2 Interrupt Flag bit                                                                                                                              |                  |                   |               |                 |             |              |        |  |  |

|         | Capture mode:                                                                                                                                                |                  |                   |               |                 |             |              |        |  |  |

|         | 1 = A TMR1 register capture occurred (must be cleared in software)                                                                                           |                  |                   |               |                 |             |              |        |  |  |

|         |                                                                                                                                                              | IR1 register ca  | apture occ        | urred         |                 |             |              |        |  |  |

|         | $\frac{\text{Compare r}}{1 - 4}$                                                                                                                             |                  | mara mat          | ab accurred   | (must be clear  | od in coffu | <b>ar</b> a) |        |  |  |

|         |                                                                                                                                                              | IR1 register co  |                   |               | (must be cleare |             | are)         |        |  |  |

|         | PWM mod                                                                                                                                                      |                  |                   |               | -               |             |              |        |  |  |

|         | Unused                                                                                                                                                       |                  |                   |               |                 |             |              |        |  |  |

|         |                                                                                                                                                              |                  |                   |               |                 |             |              |        |  |  |

|         |                                                                                                                                                              | Figu             | re 0-6 <b>P</b> H | R2 register   | for PIC16F877   | 7           |              |        |  |  |

|         |                                                                                                                                                              | _                |                   |               |                 |             |              |        |  |  |

|         | U-0                                                                                                                                                          | R/W-0            | U-0               | R/W-0         | R/W-0           | U-0         | U-0          | R/W-0  |  |  |

|         | _                                                                                                                                                            | Reserved         | —                 | EEIE          | BCLIE           | _           | _            | CCP2IE |  |  |

|         | bit 7                                                                                                                                                        |                  |                   |               |                 |             |              | bit 0  |  |  |

|         |                                                                                                                                                              |                  |                   |               |                 |             |              |        |  |  |

- bit 7 Unimplemented: Read as '0'

- bit 6 Reserved: Always maintain this bit clear

- bit 5 Unimplemented: Read as '0'

- bit 4 EEIE: EEPROM Write Operation Interrupt Enable

- 1 = Enable EE Write Interrupt

- 0 = Disable EE Write Interrupt

- bit 3 BCLIE: Bus Collision Interrupt Enable

- 1 = Enable Bus Collision Interrupt

- 0 = Disable Bus Collision Interrupt

#### bit 2-1 Unimplemented: Read as '0'

- CCP2IE: CCP2 Interrupt Enable bit

- 1 = Enables the CCP2 interrupt

- 0 = Disables the CCP2 interrupt

#### Figure 0-7 PIE2 register for PIC16F877

The RB0/INT Interrupt and RB Port Change Interrupt are the microcontroller's open eyes to the external world. Even I've heard rumors at piclist about the non realiable RB Port Change Interrupts, every time I've used those interrupts I was satisfied. The purpose of interrupt on change are to check the changing state of the port B4...B7 for fast or slow events. There aren't good olnly for **changing state** detection so don't try to use them like using the RB0 interrupt because will not work. Don't try also to detect fast events using pure JAL and portB change interrupt because will probably don't work also. But in pure assembler under JAL will be fine.

The RB0 interrupt it's perfect for mains zero cross detection (like will see in Lesson 3) or other external commands (like wake up from sleep on various external events). Using an external logic, the RB0/INT may be multiplexed to as many inputs we need, using the same scheme presented in figure 0.3 for peripheral interrupts inside the PIC.

There are minor differences in naming the interrupt bits which belongs to the interrupt registers, in various PIC microcontrollers. But the bits function are almost the same. For example the interrupt register from PIC12F675. You may notice only the GPIF and GPIE differences against RBIF and RBIE from the other midrange PIC microcontrollers.

I've heard about many programs claiming they can transform the PIC into a multitasking tool using the interrupts in a fancy way. I have doubts there is an universal solution for using interrupts. However, a good starting point for understanding interrupts will be also:

AN585 – A Real-Time Operating systems for PIC micro Microcontrollers

AN576 – Tehniques to Disable Global Interrupts

AN566 – Using the PortB Interrupt on Change as an External Interrupt

All this application notes can be found in Embedded Control Handbook, voll edited by Microchip, or on <u>http://www.microchip.com</u>