# Introducción a las Computadoras

Capítulo 3 Buses del Sistema

# Concepto de Programa

- Los sistemas de propósito espcífico no son flexibles

- El Hardware de propósito general puede realizar diferentes tareas, dadas las señales de control correctas

- En lugar de reconstruir un sistema, se le da un conjunto nuevo de señales de control

# ¿Que es un programa?

- Una secuencia de pasos

- En cada uno, se realiza una operación lógica o aritmética

- Cada operación necesita un conjunto diferente de señales de control

#### Función de la Unidad de Control

- Para cada operación se provee un único código

—Ej. ADD, MOVE

- Una parte del hardware, acepta el código y genera las señales de control

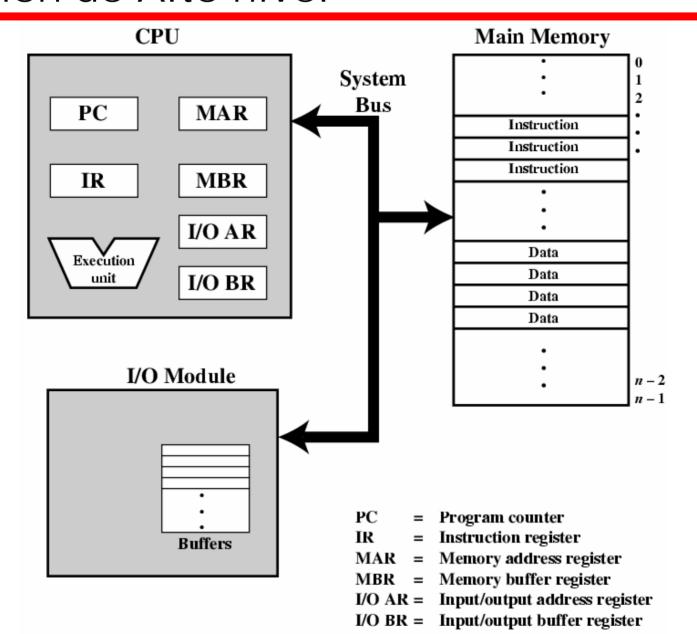

#### Componentes

- La Unidad de Control y la Lógica Aritmética constituyen la Unidad Central de Procesamiento

- Los Datos e Instrucciones necesitan ingresar y los resultados salir del sistema

- —Entrada/Salida

- Es necesario un almacenamiento temporal del código y los resultados

- —Memoria principal

# Componentes de la Computadora: Visión de Alto nivel

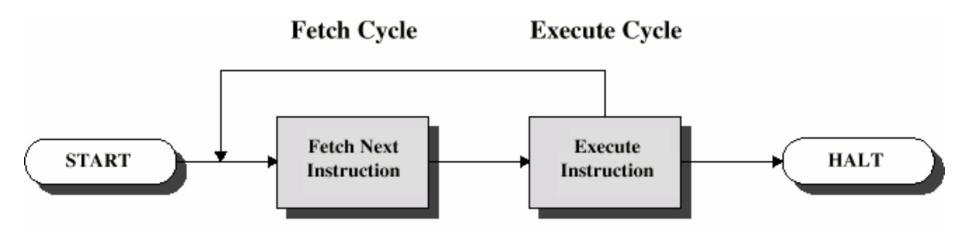

#### Ciclo de instrucción - Indivisible

- Medido según la cadencia de un reloj

- Dos pasos:

- —Captación (Fetch)

- —Ejecución

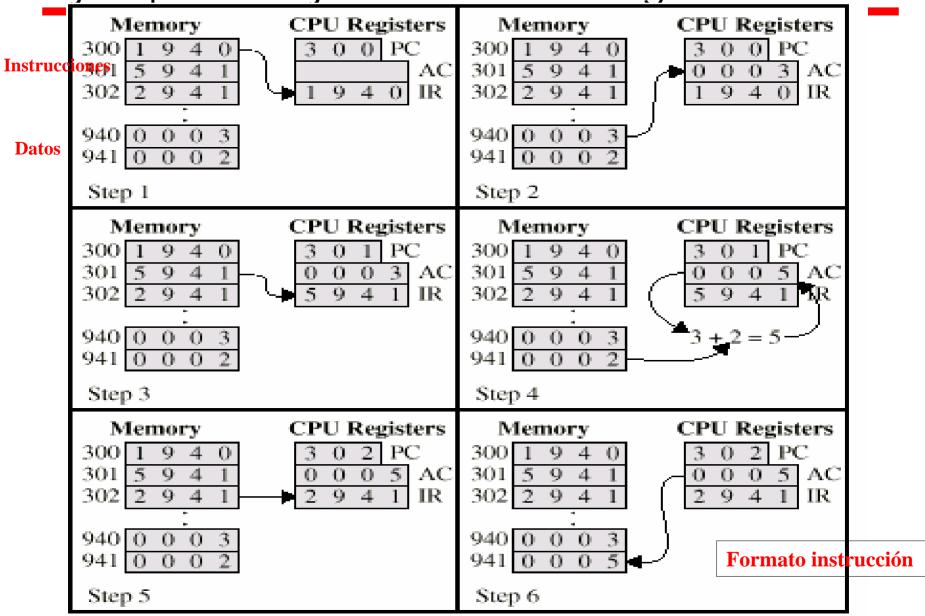

# Ciclo de Captación

- El Contador de Programa (PC) contiene la dirección de la próxima instrucción a captar

- El procesador capta la instrucción de memoria apuntada por el PC

- Incrementa el PC (PC=PC+1)

- —A menos que se indique otra cosa

- La instrucción se carga en el Registro de Instrucción (IR)

- El procesador (UC) interpreta la instrucción (decodifica) y realiza las acciones requeridas

## Ciclo de Ejecución - Tipos básicos

- Trasferencia procesador-memoria

- —Datos son transferidos entre la CPU y la memoria principal

- Transferencia procesador E/S

- —Datos transferidos entre CPU y modulo de E/S

- Procesamiento de Datos

- Operaciones lógicas o aritméticas con los datos

- Control

- —Alteración de la secuencia de operaciones

- —Ej. jump

- Combinaciones de lo anterior

Ejemplo de Ejecución del Programa

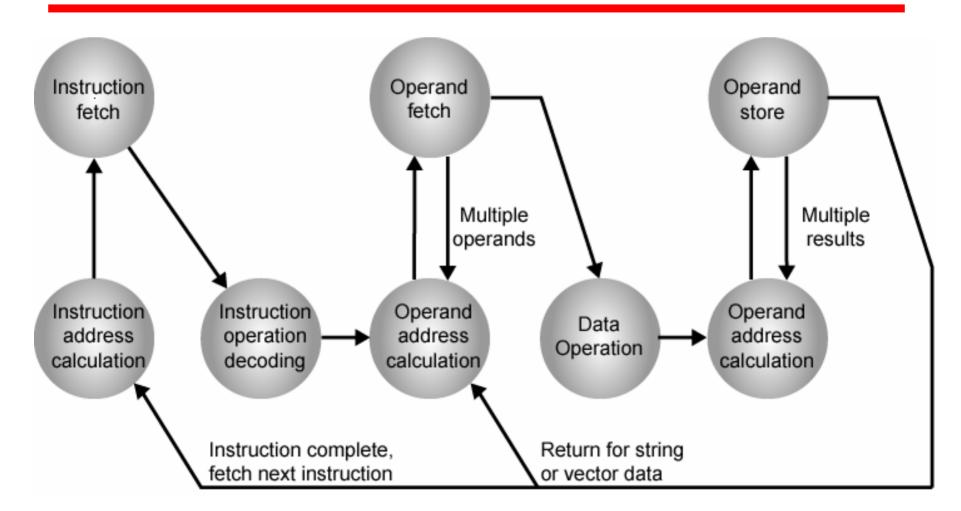

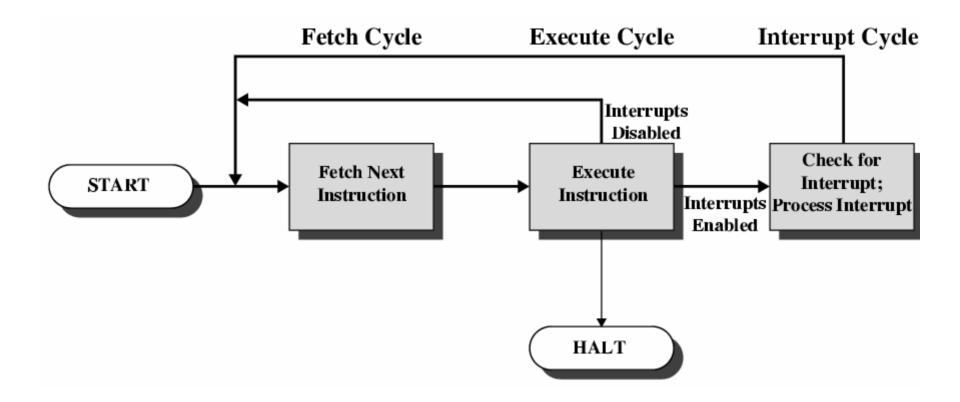

## Diagrama de estado del Ciclo de Instrucción

Notar los accesos a memoria o E/S

#### Interrupciones

- Mecanismo por el cual otros módulos (Ej. E/S) pueden interrumpir la secuencia normal de procesamiento

- Por software

- Ej. Desbordamiento (overflow), división por cero

- Por un temporizador

- Generada por el temporizador interno del sistema

- Utilizado para multitarea pre-emptive (prevista)

- Por la E/S

- Desde un controlador E/S

- Por una falla del hardware

- Ej. Error de paridad de memoria

Concepto de subrutina y funciones Mapa de memoria lineal

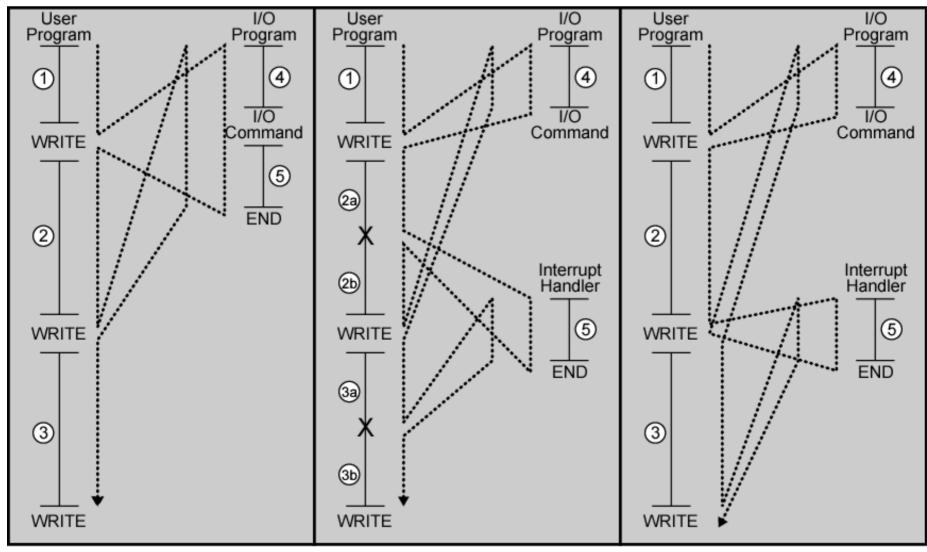

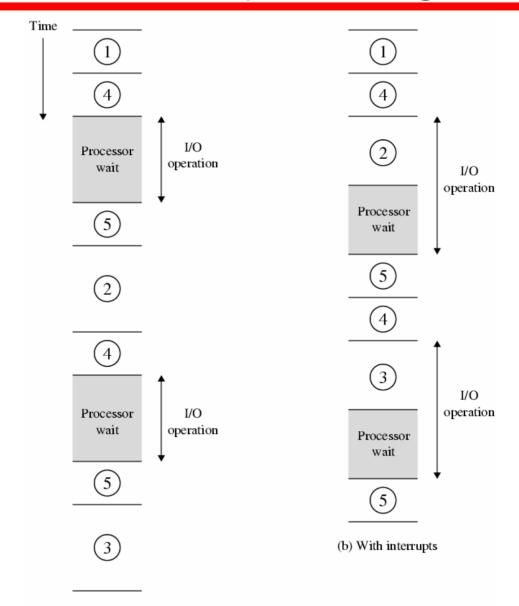

## Control de Flujo del Programa

(a) No interrupts

(b) Interrupts; short I/O wait

(c) Interrupts; long I/O wait

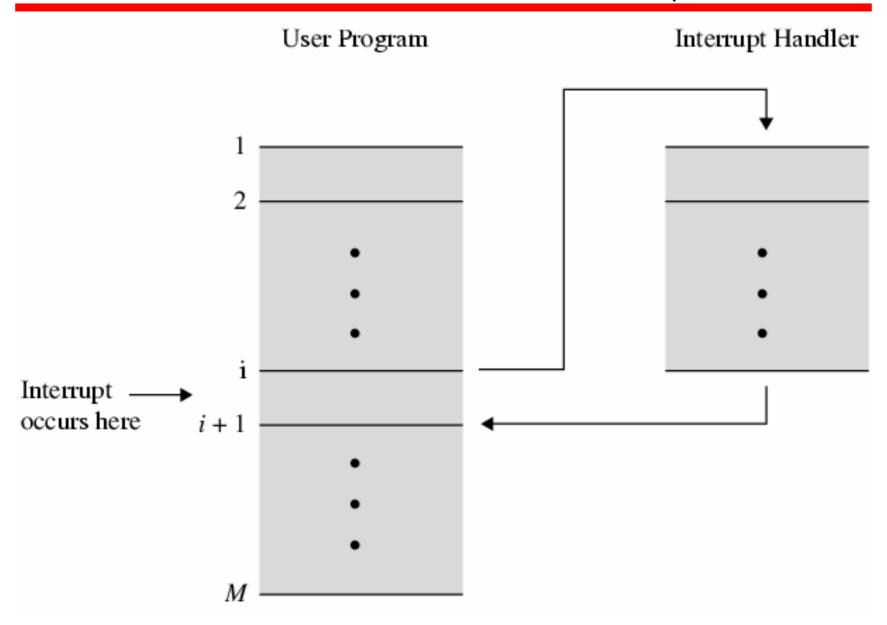

## Transferencia del Control con Interrupciones

#### Ciclo de Interrupción

- Se agrega un paso al ciclo de instrucción

- El procesador verifica si existe pedido de interrupción

- Indicada por una señal de interrupción (IRQ)

- Si no hay, capta la próxima instrucción

- Si hay una interrupción pendiente:

- Suspende la ejecución del proceso actual

- Salva el contexto

- Coloca en el PC la dirección de la rutina encargada de manejar la interrupción (interrupt handler)

- Se procesa la interrupción

- Restaura el contexto y continúa con el programa interrumpido

#### Ciclo de Instrucción con Interrupciones

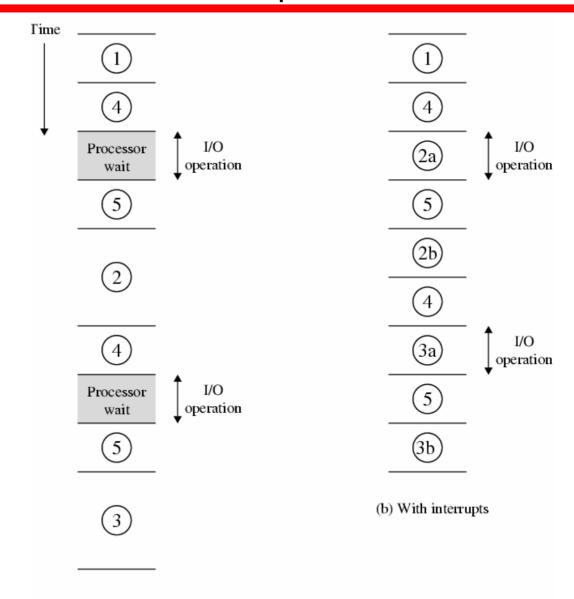

# Temporización en Espera corta de E/S

# Temporización en espera Larga de E/S

(a) Without interrupts

# Diagrama de estado con ciclo de interrupción

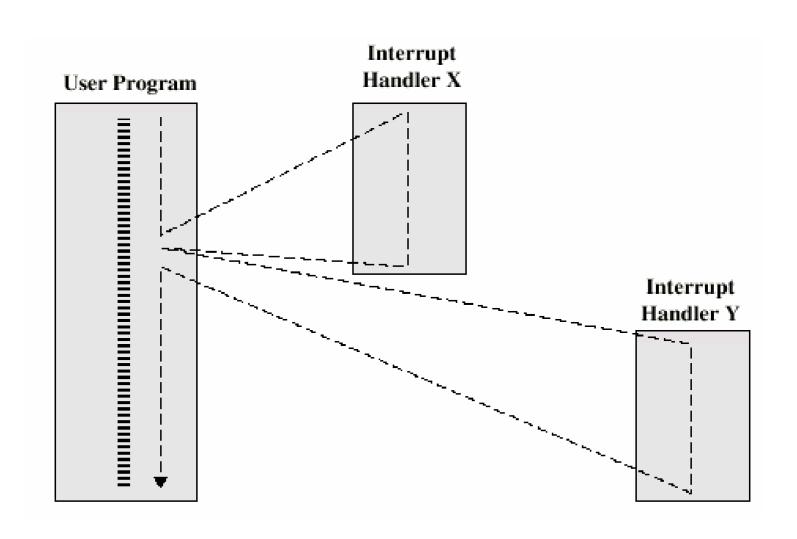

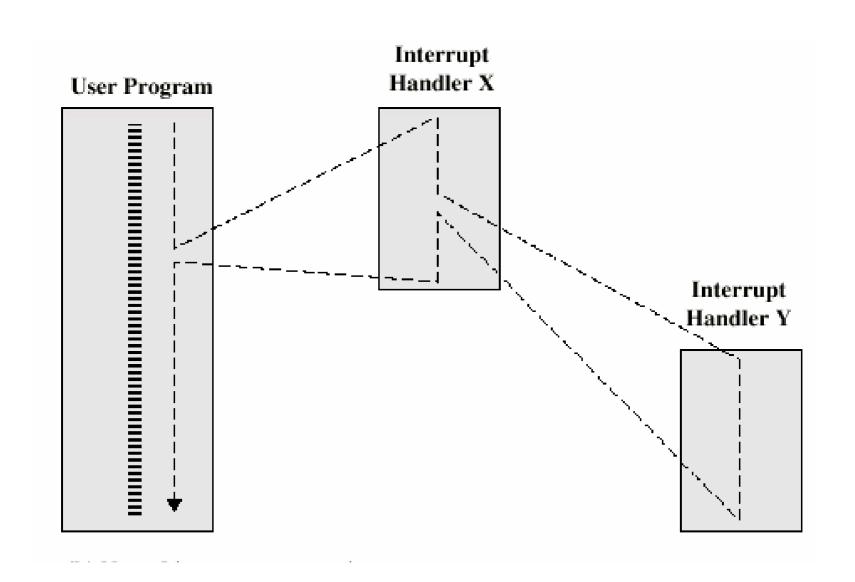

## Interrupciones Múltiples

- Interrupciones deshabilitadas

- —El procesador ignorará las otras interrupciones mientras procesa una

- —El pedido queda pendiente y es verificado después de que se finalizó la interrupción actual

- —Son procesadas en la secuencia que ocurrieron

- Si se definen prioridades

- —Las interrupciones de baja prioridad pueden ser interrumpidas por las de alta prioridad

- —Cuando se termina de procesar una interrupción de alta prioridad, se retoma la ejecución de la interrupción anterior

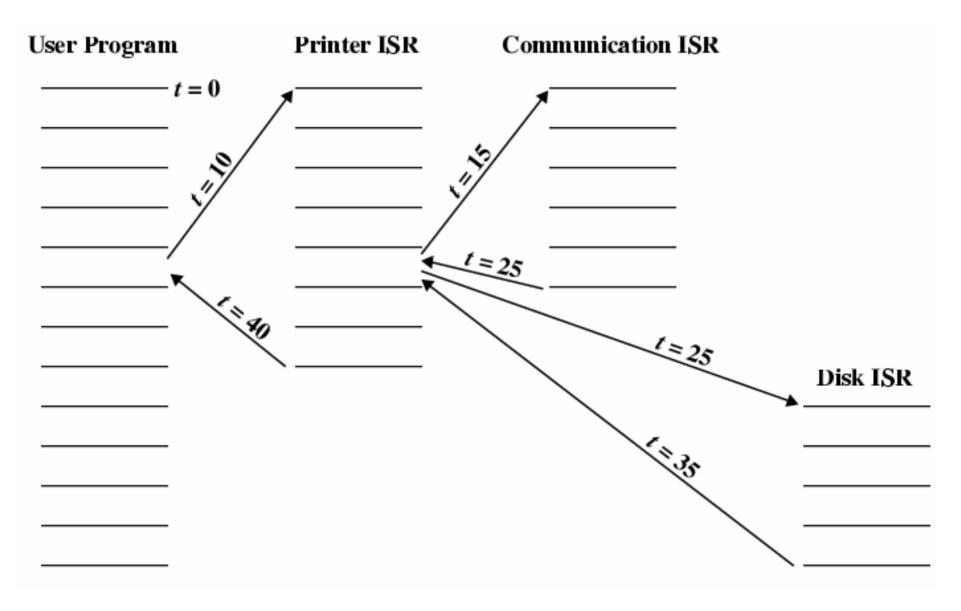

## Interrupciones Múltiples- Secuencial

## Interrupciones Múltiples - Anidadas

#### Secuencia temporal de Interrupciones Múltiples

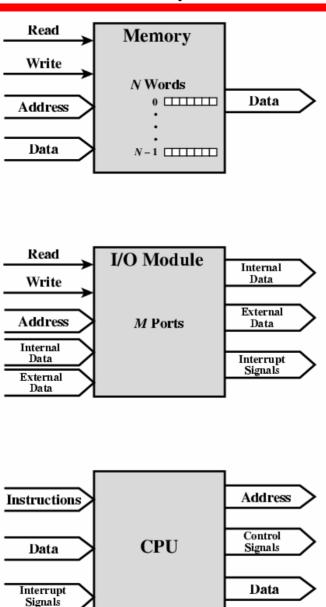

#### Estructura de interconexión

- Todas las unidades pueden deben estar conectadas

- Se necesitan distintos tipos de conexión para los diferentes tipos de unidades

- -- Memoria

- -E/S

- -CPU

# Módulos de la Computadora

#### Conexión de la Memoria

- Recibe y envía datos

- Recibe direcciones (de posiciones)

- Recibe señales de control

- —Lectura

- —Escritura

- —Temporización

# Conexión de la E/S (1)

- Similar al de la memoria para el punto de vista de la computadora

- Operación como Salida

- —Recibe datos de la computadora

- —Envía dichos datos a los periféricos

- Operación como Entrada

- —Recibe datos de los periféricos

- —Los envía a la computadora

# Conexión de la E/S(2)

- Recibe señales de control de la computadora

- Envía señales de control a los periféricos

- —Ej. Giro del disco

- Recibe direcciones de la computadora

- —Ej. Número de puerto para identificar el periférico

- Envía señales de interrupción (control)

#### Conexión de la CPU

- Lee instrucciones y datos

- Escribe datos (después del procesamiento)

- Envía señales de control a otras unidades

- Recibe (y actúa según) interrupciones

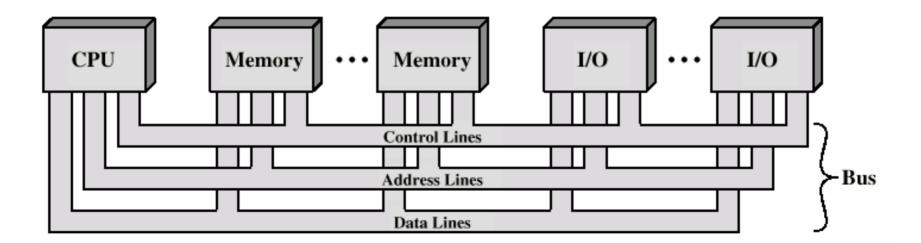

#### Buses

- Hay un numero posible de sistemas de interconexión

- Estructuras simples y múltiples de bus son las mas comunes

- Ej. Control/Direcciones/Datos (PC)

- Ej. Unibus (DEC-PDP)

#### ¿Que es un Bus?

- Un camino de comunicación entre dos o mas dispositivos

- Difusión

- Con frecuencia agrupado

- —Un número de canales en un bus

- —Ej. Bus de datos de 32 bit son 32 canales separados de 1 bit

- No se consideran las líneas de alimentación

#### Bus de Datos

- Transmite los Datos

- —Recordar que no hay diferencia entre "datos" e "instrucciones" en este nivel

- El ancho es la clave que determina su rendimiento

- -8, 16, 32, 64 bit

#### Bus de Direcciones

- Identifica el origen o el destino de los datos

- Ej. La CPU necesita leer una instrucción (datos) desde una dada locación de memoria

- El ancho determina la capacidad máxima de memoria física del sistema

- —Ej. 8080 tenía un bus de direcciones de 16 bit esto daba un espacio de direcciones de 64k

#### Bus de control

- Controla y temporiza las transferencias

- —Señal de lectura/escritura en memoria

- —Pedido de Interrupción

- -Señales de Reloj

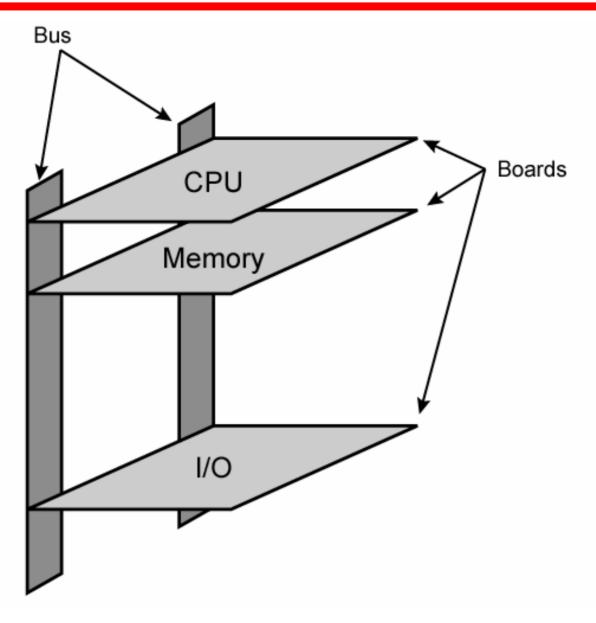

#### Esquema de Interconexión con Bus

### Apariencia

- Como son?

- Líneas de cobre paralelas en las placas

- —Cables planos

- —Conectores en placas

- PCI

- —Conjunto de cables

# Implementación del bus

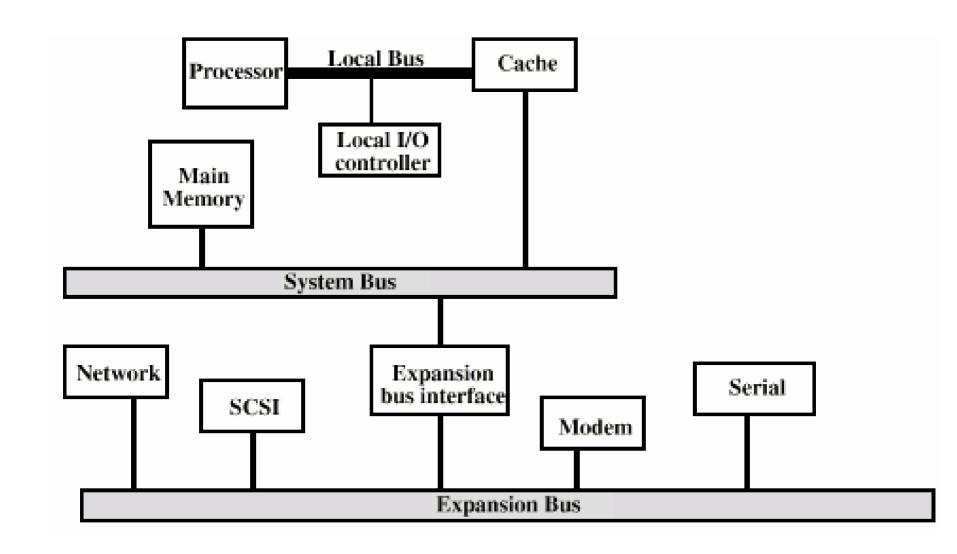

### Problemas de los buses simples

- Muchos dispositivos en un solo bus llevan a:

- -Retardos de propagación

- Determina el tiempo que necesitan los dispositivos para coordinarse en el uso del bus. Si el control pasa con frecuencia de un dispositivo a otro, esto afecta las prestaciones

- Se puede aumentar el ancho o la velocidad, pero también mejoran los periféricos

- La mayoría de los sistemas utilizan Buses Múltiples

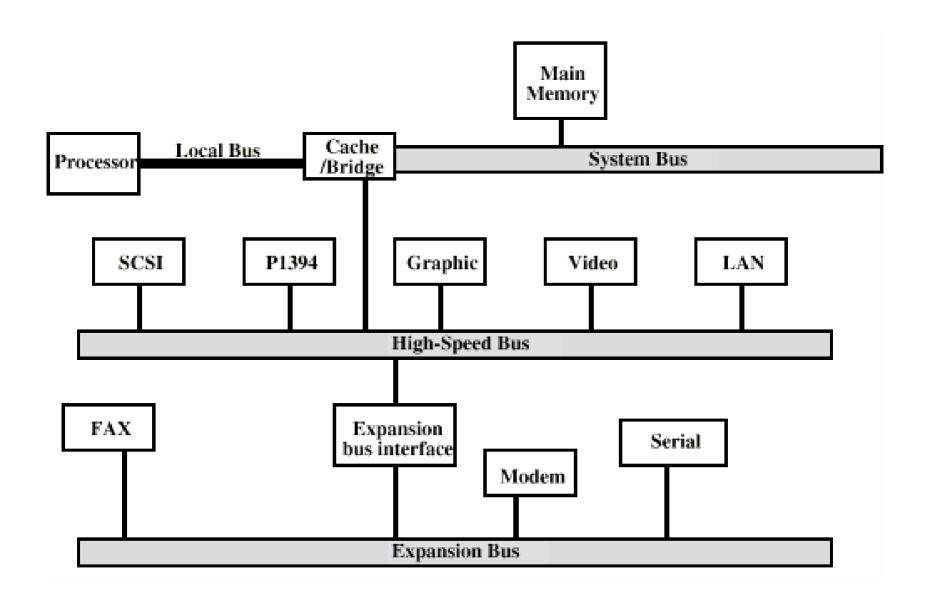

## Tradicional (ISA)(con cache)

#### Bus de Alto Rendimiento

#### Tipos de Buses

- Dedicados

- —Líneas separadas para datos y direcciones

- Multiplexados

- —Líneas compartidas

- —Se valida una dirección o datos con una línea de control

- —Ventaja- pocas líneas

- —Desventajas

- Control se hace mas complejo

- Cae el rendimiento

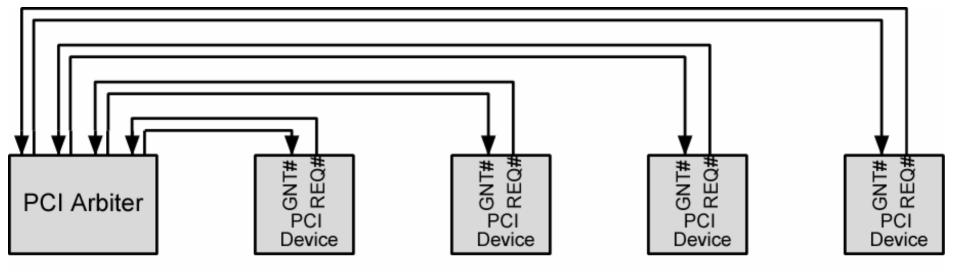

## Arbitraje del Bus

- Mas de un módulo puede controlar el bus

- Ej. CPU y controlador DMA

- Solo un módulo puede tener el control del bus a la vez

- Debe considerarse un arbitraje del bus:

- centralizado

- distribuido

#### Arbitraje Centralizado o Distribuido

#### Centralizado

- —Un solo dispositivo de hardware controla el acceso al bus

- Controlador de Bus

- Arbitro

- —Puede ser parte de la CPU o una unidad separada

#### Distribuido

- —Cada módulo puede pedir el bus

- —Hay lógica de control en todos los módulos

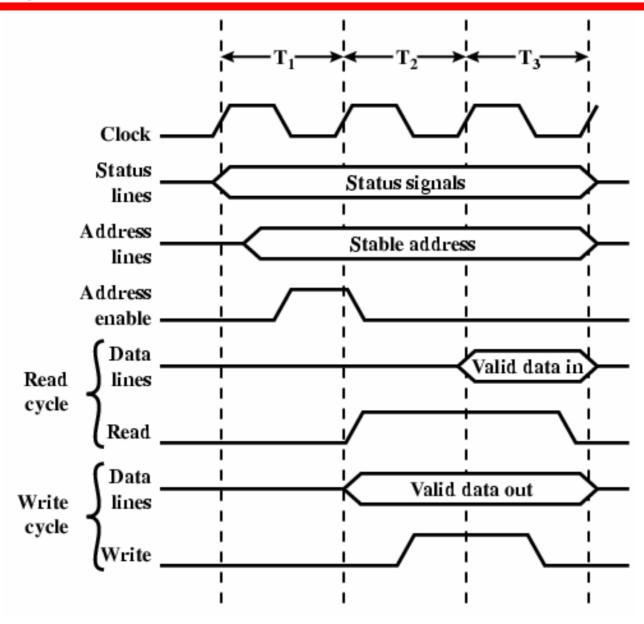

#### Temporización

- Coordinación de los eventos en el bus

- Síncrono

- —Eventos según un reloj

- —El bus de Control incluye la señal de reloj

- —Un intervalo de 1 a 0 se conoce como ciclo de bus

- —Todos los dispositivos están conectados a esta línea

- —Generalmente se sincroniza con flanco ascendente

- —Un solo ciclo por evento

# Temporización Síncrona

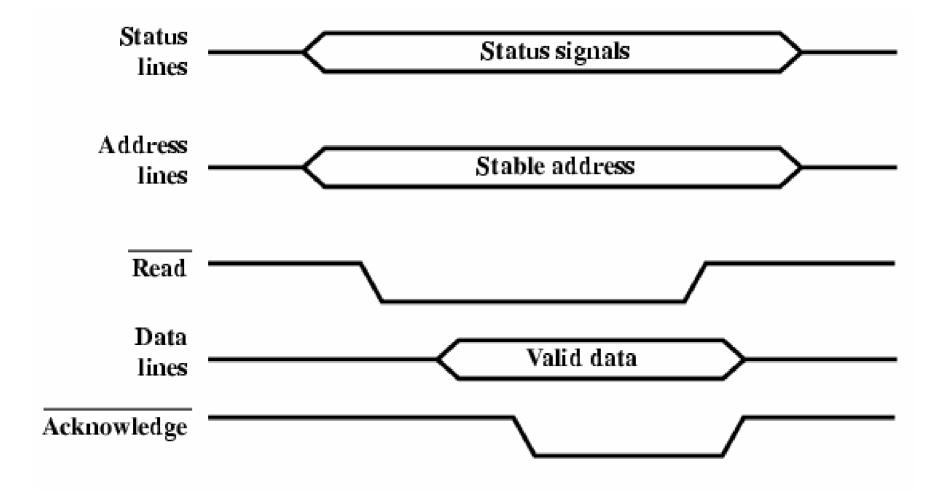

#### Temporización asíncrona - Lectura

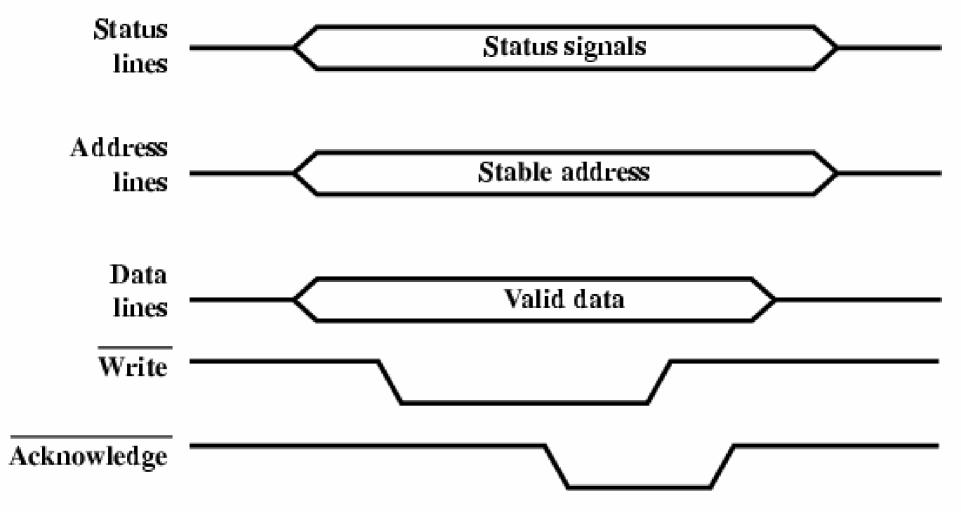

## Temporización asíncrona - Escritura

### Tipos de transferencia

- Lectura

- Escritura

- Lectura modificación escritura

- Lectura después de escritura

- Bloque (burst)

#### **Bus PCI**

- Interconexión de periféricos

- Intel la hizo de dominio público

- 32 o 64 bit

- 50 líneas

## Líneas del bus (requeridas)

- Líneas del Sistema

- —Incluyendo reloj y reset

- Direcciones y datos

- —32 líneas multiplexadas para datos/direcciones

- —Líneas de interrupción y validación

- Control de la interfase

- Arbitraje

- —No compartido

- —Conexión directa al arbitraje de bus PCI

- Líneas para errores

# Líneas del bus PCI (Opcionales)

- Líneas de interrupción

- —No compartidas

- Soporte de cache

- Extensión a 64-bit

- -32 líneas adicionales

- —Multiplexadas

- —2 líneas para habilitar dispositivos que usan esta extensión

- Testeo

- —Procedimientos de prueba según IEEE 149.1

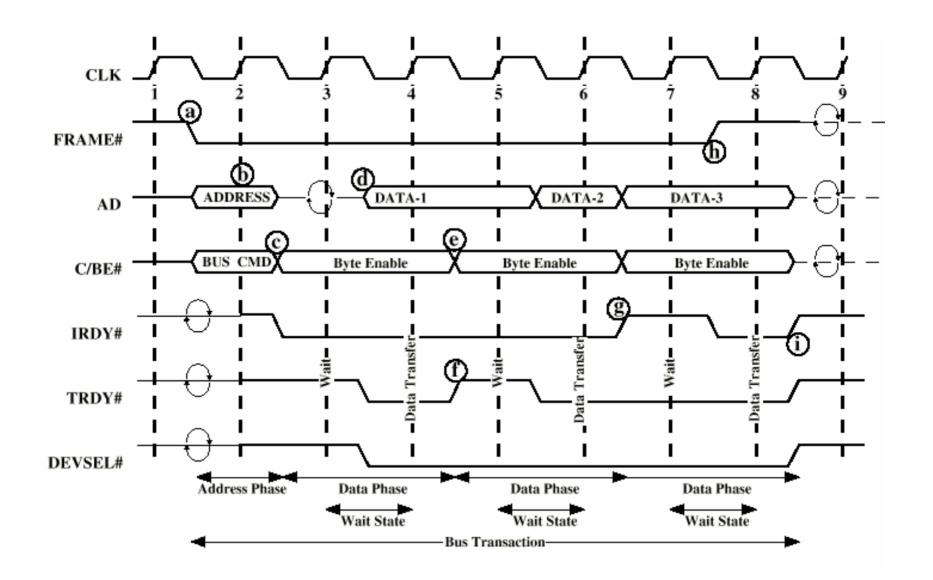

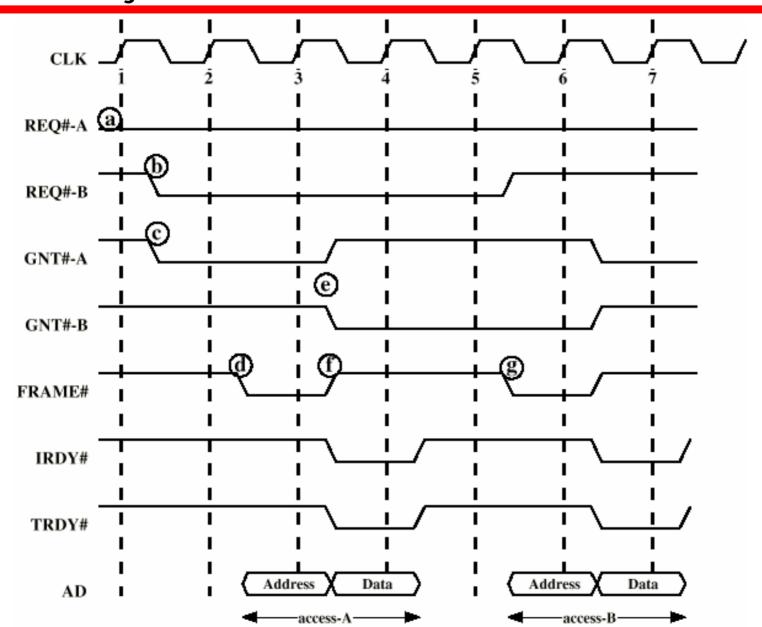

#### Comandos PCI

- Transacciones entre un iniciador (master) y un destino

- Master pide el bus

- Se termina el tipo de transacción

- —Ej. L/E o E/S

- Fase de direccionamiento

- Una o mas fases de datos

### Temporización PCI - Lectura

#### Arbitro Bus PCI

# Arbitraje PCI

#### Lecturas

- Requeridas:

- -Stallings: Capítulo 3

- Opcionales

- —www.pcguide.com/ref/mbsys/buses/

- —www.pcguide.com/